Вплив дестабілізуючих факторів на характеристики ІМС.

|

|

Дестабілізуючими факторами вважаються відхилення напруги живлення від нормального значення; відхилення від нормальних теператур;зміна навантаження на вихідному каскаді.

ΔЕж ΔТ ΔІн

Ці фактори впливають на:

- завадостікість ( Uз+, Uз- )

- споживана потужність Рс

- швидкодія, що визначає максимальну частоту переключення або час середньої затримки(fп мах, τзат)

- навант.здатності (Ін)

Відхилення напруги живлення :Еж (дозволяється змінювати її у межах ±10%)

При збільшенні Еж => зававдостійкість збільшилась

=> Рс збіл.по квадр.законі

=> fn –збільш.

=> In – збільш.

На завадостійкість ΔT практично не впливає. При зміні температури оппори мікросхеми, але в той же час збільшується коофіцієнт транзистора → ΔT практично не впливає на Pc

При збільшенні ΔT => fn - трохи збільшується

=> In залишається без змін

При збільшенні ΔIn => Uз+, Uз- зменшується

=> Рс – збільшується

=> fn зменшується за рахунок того, що наваження збільшується і в результаті перерозподіляється при перек.у вихідному каскаді став гірш.

=>In зменшуєься

Вплив ємності навантаження на швидкодію ІМС.

Сп – паразитна ємність. 1. На діодному переході вхід логічного елементу має паразитну ємність 2...4пФ. Якщо елементів багато, то ємності сумуються.

Сп – паразитна ємність. 1. На діодному переході вхід логічного елементу має паразитну ємність 2...4пФ. Якщо елементів багато, то ємності сумуються.

2. Смонтажан – ємність між доріжками. Напр. якщо t=τ. Uвих=0,63Uвх

3В≈1,9В

Початок переключення резистора за час τ:

Нехай Сн=30пФ

Rекв=1Ком -> τ=30нс, якщо транзистор відкритий, то розряд проходить швидше. Чим більша ємність навантаження, тим повільніше працює елемент.

6. Логічні ІМС КНОН та їх основні характеристики.

В процесі функціонування nМОН логічних схем, можливе протікання через логічні елементи наскрізних струмів від джерела живлення до загального проводу. З метою зменшення потужності, що споживається, бажано ліквідувати наскрізні стуми. Для цього потрібно, щоб навантажувальний транзистор Т1 відкривався та закривався у протифазі з функціональним транзистором Т2. Одним із способів реалізації цього є реалізація на кристалі як нормально-закритих, так і нормально-відкритих МОН-транзисторів. При цьому технологія виготовлення логічних елементів потребує використання додаткових технологічних операцій для імплантації іонів.

Інший метод усунення наскрізних струмів полягає у використанні компліментарних (взаємодоповнюючих) МОН-транзисторів двох типів провідності. МОН-транзистор n-типу відкривається, якщо до його заслону прикладений високий потенціал, а для того щоб відкрився МОН-транзистор p-типу, до його заслону потрібно прикласти низький потенціал. Технологія виготовлення цифрових інтегральних мікросхем, при якій використовуються МОН-транзистори обох типів провідності, називається КМОН.

Тут відсутні наскрізні струми, майже не споживає потужності в статичному режимі, вх. струми споживаються тільки для перезарядки вх. ємності заслонок.

Степені інтеграції мікросхем.

К=LgN – степінь інтеграції, де N-кількість елементарних елементів на кристалі.

Малі: N = 10 -> K = 1

N = 100 -> K = 1

Середні: N = 103 -> K = 1

N = 104 -> K = 1

Великі: N = 105 -> K = 1

N = 106 -> K = 1

N = 106 -> K = 1

КМОН складається з 2 транзисторів протилежних за провідністю.

Коли на 3 є „1” між С і В створюється канал, по якому може протікати струм, який в свою чергу закриває р-п-р транзистор.

Якщо з „0” – транзистор п-р-п закривається, то р-п-р – відкривається.

Паралельні діоди згорять якщо поміняти полярність напруги живлення.

Паралельні діоди згорять якщо поміняти полярність напруги живлення.

Основні особливості схем КМОН:

1. Високий вхідний опір (1010Ом і більше)

2. Високий коефіцієнт розгалуження

3. Низький вихідний опір в порівнянні з вхідним

4. Рівні логічних 0 та 1 ТТЛ та КМОН

ІМС КМОН працюють в широкому діапазоні напруг живлення (3-15В)

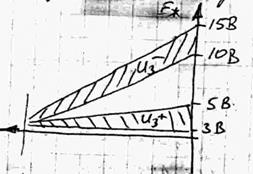

Висока завадостійкість. В залежності від вхідної напруги змінюється завадостійкість.

Практично незалежність основних параметрів ІС від дестабілізуючих факторів (для температури та навантаження).

Діапазон робочих температур: -60+125С

Напруга живлення впливає на завадостійкість і швидкодію (при збільшенні Еж збільшується швидкодія елемента КМОН)

Передавальна Вхідна характеристика

вихідна характеристика

Чим більший струм на вході – тим більший спад напруги.

|

© 2013 wikipage.com.ua - Дякуємо за посилання на wikipage.com.ua | Контакти |