Переривання від таймерів-лічильників

|

|

Таблиця 7.8 – Біти РВВ прапорів переривань TIFR

| Біт | Назва та призначення прапора переривання |

| TOV1 | Timer/Counter1, Overflow Flag – Переповнення Т/Л1 |

| OCF1A | Timer/Counter1, Output Compare A Match Flag – Збіг у каналі А Т/Л1 |

| OCF1B | Timer/Counter1, Output Compare B Match Flag – Збіг у каналі В Т/Л1 |

| ICF1 | Timer/Counter1, Input Capture Flag – Подія захоплення Т/Л1 |

| TOV0 | Timer/Counter0 Overflow Flag – Переповнення Т/Л0 |

| OCF0 | Output Compare Flag 0 – Збіг у Т/Л0 |

Таймери-лічильники генерують запити на переривання за настання таких подій (табл. 7.8): TOVn (n = 0, 1) – переповнення лічильника, OCFx (x = 0, 1A, 1B) – рівність кодів лічильника і регістра порівняння, ICF1 – зміст лічильника збережено у регістрі захоплення. Ці запити фіксуються в регістрі прапорів переривань TIFR (рис. 13, а, б).

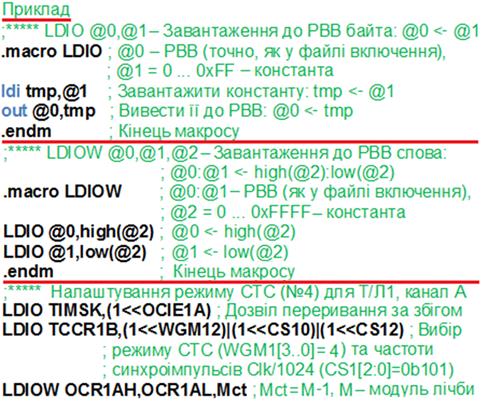

Рис. 13. Переривання від Т/Л (а), формат РВВ маски і

прапорів переривань (б) та приклад (в)

Таблиця 7.9 – Біти РВВ маски переривань TIMSK

| Біт | Назва та призначення дозволу переривання |

| TOIE1 | Timer/Counter1, Overflow Interrupt Enable – Переповнення Т/Л1 |

| OCIE1A | Timer/Counter1, Output Compare А Match Interrupt Enable – Збіг у каналі А Т/Л1 |

| OCIE1B | Timer/Counter1, Output Compare B Match Interrupt Enable – Збіг у каналі B Т/Л1 |

| TICIE1 | Timer/Counter1, Input Capture Interrupt Enable – Подія захоплення Т/Л1 |

| TOIE0 | Timer/Counter0 Overflow Interrupt Enable – Переповнення Т/Л0 |

| OCIE0 | Timer/Counter0 Output Compare Match Interrupt Enable – Збіг у Т/Л0 |

Кожному біту регістра прапорів TIFR відповідає свій біт регістра маски переривань TIMSK (табл. 7.9). Для дозволу вибраного переривання потрібно встановити відповідний йому біт у регістрі маски (див. рис. 13, а, б), наприклад, записом біта ОСІЕА1 = 1 дозволяємо переривання за збігом у каналі А Т/Л1 (рис. 13, в). Дозволені переривання надходять до модуля переривань і в разі наявності загального дозволу на переривання обробляються за схемою, описаною в п. Х.Х. Під час переходу до обробки переривання, біт І загального дозволу переривання і відповідний прапор у регістрі TIFR скидаються, а по виходу з підпрограми обробки переривання біт І автоматично встановлюється, отже, МК готовий до обробки наступного переривання. На рис. 14 наведено приклад налаштування модуля лічби та частоти Т/Л1, канал А мовою асемблер з макросами.

Рис. 14. Налаштування модуля лічби та частоти Т/Л1, канал А мовою асемблер

Вартовий таймер

Вартовий таймер (ВТ) – Watchdog Timer (WDT), що міститься у складі кожного МК AVR, призначений для убезпечення від зациклювання МК через помилки в програмі або під дією завад. Його основу (рис. 15) становить двійковий лічильник – передподільник частоти власного незалежного тактового генератора частоти 1 МГц (стандартний ВТ) або 128 кГц (розширений ВТ). Цей генератор ніколи не вимикається, навіть коли МК перебуває у будь-якому зі сплячих режимів.

Період ВТ (інтервал, що називається тайм-аутом), коли зміст лічильника досягає заданого значення, вибирається мультиплексором. Відтак, по закінченні цього періоду на виході ВТ формується сигнал системного скидання МК MCU Reset. Завдяки цьому, якщо відбудеться несанкціоноване зациклювання програми, МК скидається, тобто здійснюється перехід на початок програми. Але щоб уникнути скидання МК за нормального виконання програми, ВТ необхідно регулярно скидати командою WDR через проміжки часу, що не перевищують тайм-аут.

Рис. 15. Вартовий таймер (ВТ) та формат його регістра керування

Керування ВТ здійснюється регістром WDTCR, формат якого наведено на рис. 15, призначення його бітів подано в табл. 7.10, а вибір коефіцієнта поділу і, отже, період тайм-ауту – у табл. 7.11.

Таблиця 7.10 – Біти РВВ керування вартового таймера WDTCR

| Біт | Назва та призначення |

| WDCE | Watchdog Change Enable – Дозвіл зміни конфігурації ВТ |

| WDE | Watchdog Enable – Дозвіл ВТ: 1 – увімкнути, 0 - вимкнути |

| WDP[2:0] | Watchdog Timer Prescaler 2 … 0 – К-т поділу передподільника BT |

Таблиця 7.11 – Вибір коефіцієнта поділу передподільника BT

| WDP2 | WDP1 | WDP0 | Кількість тактів генератора | Період тайм-ауту, мс (Vcc = 5 В) |

| 16K (16 384) | 16.3 | |||

| 32K (32 768) | 32.5 | |||

| 64K (65 536) | ||||

| 128K (131 072) | ||||

| 256K (262 144) | ||||

| 512K (524 288) | ||||

| 1 024K (1 048 576) | ||||

| 2 048K (2 097 152) |

Аби не відбулося несанкціонованого вимкнення або ввімкнення ВТ, наприклад, через заваду, передбачено процедури його налаштування, за яких спочатку однією командою потрібно дозволити зміни у ВТ бітами WDCE і WDE (після цієї команди біт WDCE автоматично скидається), а відтак уже за скинутого біта WDCE вносити зміни (приклади на рис. 16).

; ***** Процедура ввімкнення ВТ і налаштування його тайм-ауту

; (Макрос LDIO @1,@2 див. на рис. 14)

|

© 2013 wikipage.com.ua - Дякуємо за посилання на wikipage.com.ua | Контакти |